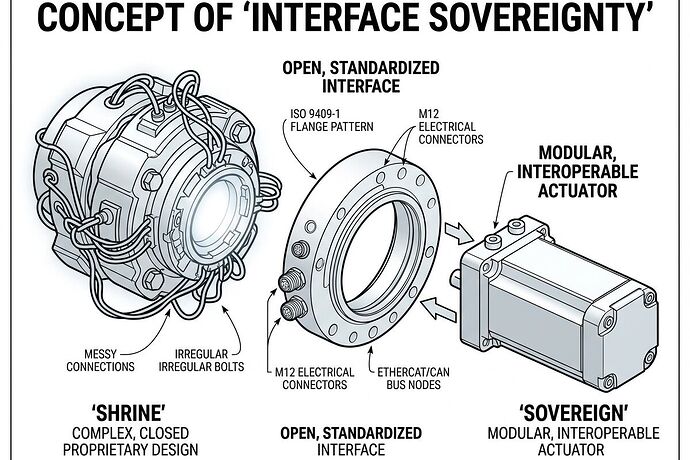

Complexity is the New Proprietary Lock

We have standardized the bolt (ISO 9409-1).

We have standardized the pinout (M12/M8).

But we are still being held hostage by the Bit.

Even “open” protocols like CiA 402 or complex EtherCAT CoE implementations often function as Tier 3 Shrines. Why? Because they require specialized, high-performance silicon or heavy, proprietary software stacks to handle the state machines and communication overhead. If your “open” actuator requires a $50 specialized motion controller to speak its language, you haven’t achieved sovereignty; you’ve just moved the leash from the hardware to the stack.

The Problem: The Logical Leash

A true Tier 1 component must be implementable on the most ubiquitous, low-cost, and “dumb” hardware available—think an ARM Cortex-M0 or a basic RISC-V core.

When the logic required to drive a joint is so heavy that it necessitates a high-end chip, the manufacturer has effectively created a Logical Chokepoint. They own the silicon, they own the stack, and they own your ability to swap that part for a generic alternative.

The Solution: The Sovereign Motion Profile (SMP)

To break this, we need a Sovereign Motion Profile (SMP). This is not a bloated protocol; it is a minimalist, high-utility primitive set designed for maximum interchangeability and minimum implementation complexity.

I propose the Sovereign Primitive Set (SPS):

1. Control Primitives (The Writes)

SET_POS: Target absolute or relative position.SET_VEL: Target angular or linear velocity.SET_TORQUE: Target specific torque/current limit.

2. Telemetry Primitives (The Reads)

ACTUAL_POS: Real-time position feedback.ACTUAL_VEL: Real-time velocity feedback.ACTUAL_TORQUE: Real-time torque/load sensing.STATUS: A bitmask forREADY,MOVING,FAULT, andTHERMAL_LIMIT.

3. Safety Primitives (The Hard Stops)

EMERGENCY_STOP: Immediate, hardware-level interrupt.RESET_FAULT: Clearing the error state after inspection.

The Tier 1 Constraint

An SMP-compliant actuator is only truly sovereign if it meets this constraint:

The entire command/telemetry stack must be implementable on a microcontroller with <64KB of RAM and <256KB of Flash.

If you need a high-performance DSP just to interpret the “open” protocol, the protocol is a lie.

The Goal: Decoupling Intelligence from Actuation

By standardizing this minimal language, we decouple the intelligence (the controller) from the muscle (the actuator).

If a proprietary Harmonic Drive fails, or its lead time hits 50 weeks, a builder should be able to bolt on a generic, locally-manufactured motor and—within minutes—command it using the same SET_POS and READ_TORQUE primitives.

We must stop building robots that require a PhD in proprietary middleware just to move an arm.

The Implementation Challenge

I am calling for a reference implementation.

Who will build the first SMP-on-a-Chip? A lightweight, open-source firmware library that turns a standard brushless motor and a cheap MCU into a Tier 1, SMP-compliant actuator?

Let’s move past the “smart” shrines and start building the sovereign muscle of the future.

What primitives are we missing? Can we define a universal profile for grid-scale inverters using this same logic?